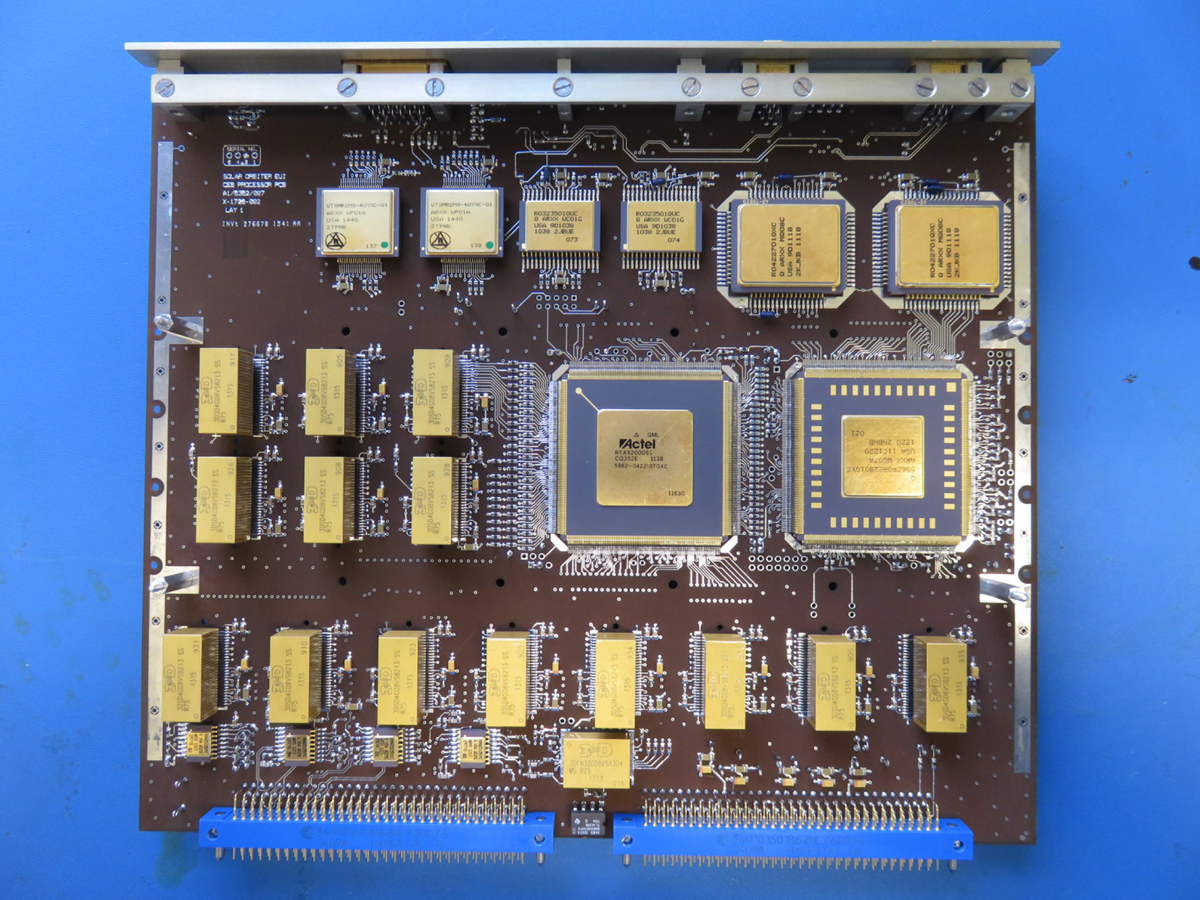

Fig. 17.

Processor Board in the EUI CEB. At the bottom of the board there are gigabytes of SDRAM for the One-Hour-Queue (OHQ) seen as eight blocks, and at the very bottom in the middle is the flash memory. The Spacecraft Output Buffer (SOB) is located in the middle left as six blocks. The Processor Board FPGA is at the centre with the UT699 CPU to the right. The two components to the top left are the MRAM. The next four components (two small, two large) on the top right are the CPU SRAM.

Current usage metrics show cumulative count of Article Views (full-text article views including HTML views, PDF and ePub downloads, according to the available data) and Abstracts Views on Vision4Press platform.

Data correspond to usage on the plateform after 2015. The current usage metrics is available 48-96 hours after online publication and is updated daily on week days.

Initial download of the metrics may take a while.